|

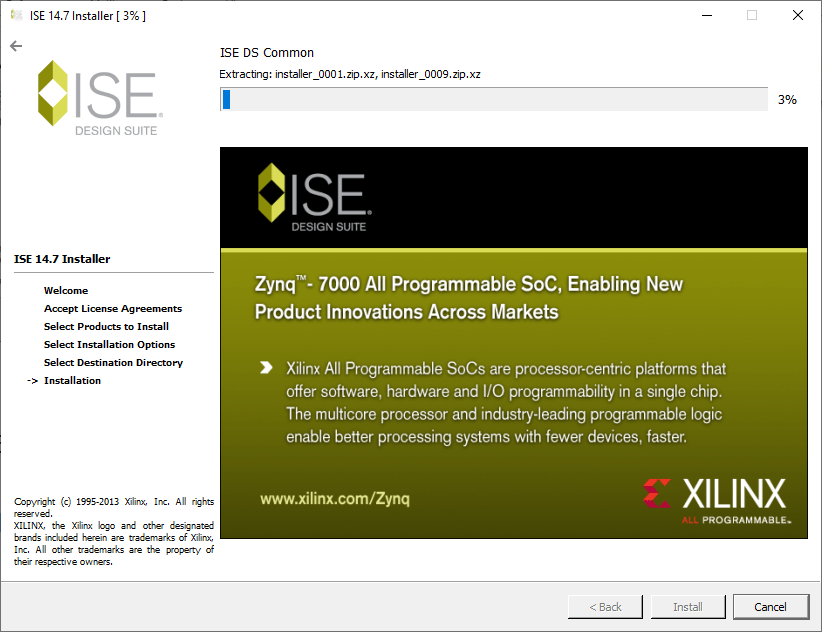

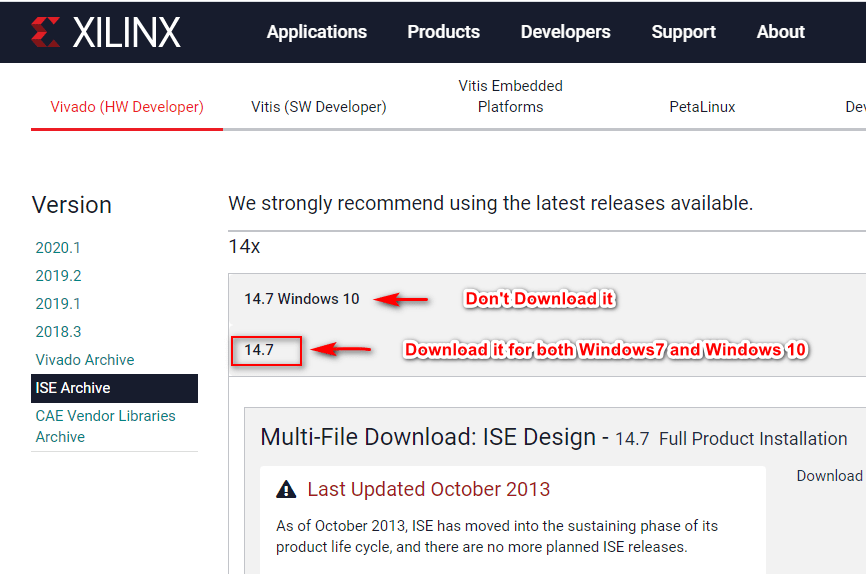

We will use hierarchy to design the 4-bit adder. Once you have derived these equation, you may verify and implement them using the Xilinx software. 1Ģ 2 Design of a 4-bit Adder Circuit Before designing a schematic, you must derive Boolean equations for your circuit. Synthesizing, Implementing and reconfiguring the FPGA chip.

Connecting the 4-bit Adder to I/O of the FPGA board. Using the Full Adder Macro Symbols to design a 4-bit adder based on Schematic Capture. Transforming the Full Adder design into a Macro Symbol. Designing a Full Adder by using the Half Adder as a component. In this tutorial you will learn the following topics: 1. Tutorial on Using Xilinx ISE Design Suite 14.6 (Design Entry using VHDL Full Adder ).

Tutorial on Using Xilinx ISE Design Suite 14.6 (Behavioral Simulation of a Half Adder Circuit). Tutorial on Using Xilinx ISE Design Suite 14.6 (Design Entry using Schematic Capture Half Adder ). At this point, the student should have read and understood the following documents: 1. 1 TUTORIAL On USING XILINX ISE DESIGN SUITE 14.6: Mixing VHDL and Schematics Design of 4-bit Ripple Carry Adder Using the Spartan-6 (NEXYS3 Board) Shawki Areibi January 11, Introduction The objective of this tutorial is to show you how VHDL can be integrated with Schematic Capture to implement complex designs using Xilinx ISE tools.

0 Comments

Leave a Reply. |

RSS Feed

RSS Feed